计算机基础:深度解析与系统协作

系列收官篇。我们从单个组件抽身出来,看整台机器:CPU、缓存、内存、存储、IO、加速器是怎么连在一起的;为什么硬件感知的代码能快 100 倍;怎么读 perf 计数器;以及计算的下一站——chiplet、硅光、量子。

前面五章,我们一个一个把盒子打开看:CPU、缓存层级、存储、主板和显卡、网络和电源。每一部分单看都很有意思,但一台计算机不是它的零件之和。一台计算机,是这些零件每一纳秒都要协商一次"接下来做什么"的那个过程。

这一章讲的就是这场对话。我们会把所有东西连成一张图,再换上 profiler 的眼睛去看这台机器;回头看那条已经存在了 80 年、至今仍在塑造每一颗芯片的设计张力;最后向前看——chiplet、硅光互连,以及悄悄走来的量子时代。

如果整个系列你只打算读一章,就读这一章。脑中的那个模型,会在这里真正合上。

第一部分 —— 一张图看完整台机器

按下电源键的那一刻,一段编排极其精密的舞蹈开始了,而且直到关机才会停。主板的 BIOS/UEFI 按顺序拉起各路电压;CPU 从硬连线的复位向量开始取指;内存控制器训练 DRAM;启动盘把内核流式装入;GPU 初始化显示引擎;网卡协商链路速率。几秒钟之内,几十亿个晶体管已经合作着把登录界面送到了你眼前。

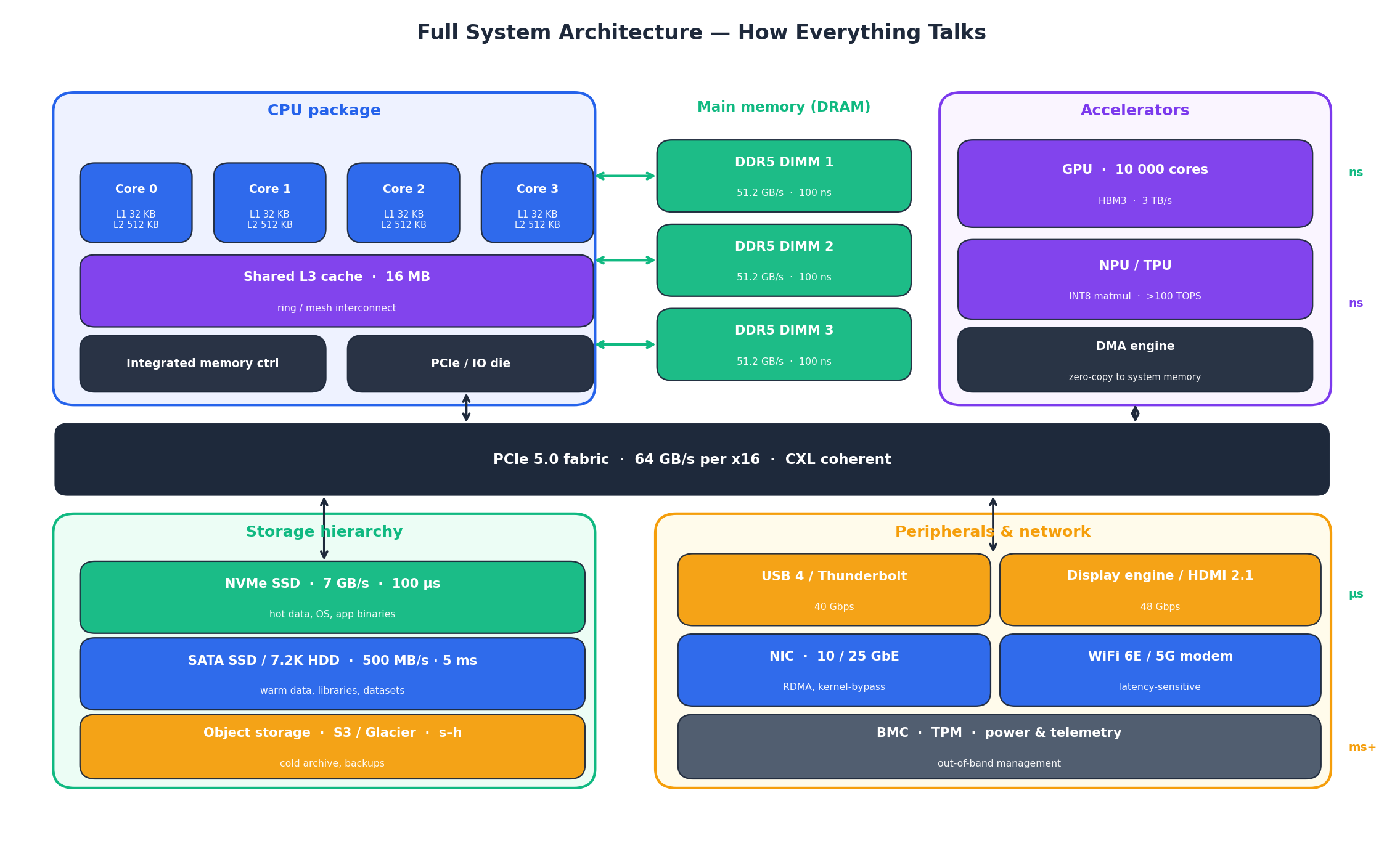

这台机器的内部结构画成一张方块图大概是这样:

图里有几件事值得停下来看看:

- 延迟梯度从左到右、从上到下逐级放大。 CPU 内部的缓存以纳秒回应,DRAM 以几十纳秒回应,PCIe 总线和加速器以几百纳秒到微秒回应,存储和网络以微秒到毫秒回应。五个数量级的延迟,挤在同一块主板上。

- PCIe 总线是脊梁。 几乎所有走出 CPU 封装的东西——GPU、NVMe SSD、网卡、USB 控制器——都从这里走。CXL 正在把这条总线扩展成"缓存一致"的内存总线,于是机架级别的"内存池化"突然变得可行。

- 再也没有"那一条总线"了。 CPU 封装内部,核之间走环形或网格;内存控制器和 IO 是独立的 die;GPU 有自己的 HBM。过去那条共享的高速公路,已经变成了一座由许多重叠网络组成的城市。

这样看完,很多坊间传闻就不再神秘。“为什么我把 SSD 换到另一个 M.2 槽,游戏就变快了?"——因为那个槽直连 CPU,另一个要走芯片组。“为什么 AI 工作负载离不开 HBM?"——因为 GPU 一秒要喂 3 TB 数据,DDR5 撑死给你 50 GB/s。“为什么小文件 mmap 这么快?"——因为它已经在 page cache 里坐着了,你付的是纳秒,不是微秒。

第二部分 —— 懂硬件的代码,能快 100 倍

硬件工程师花了五十年时间造出了一台令人发指的机器。大部分软件却仍然把它当成 1990 年代的 PC 来用。弥合这条鸿沟,是性能工程里杠杆率最高的一项技能。

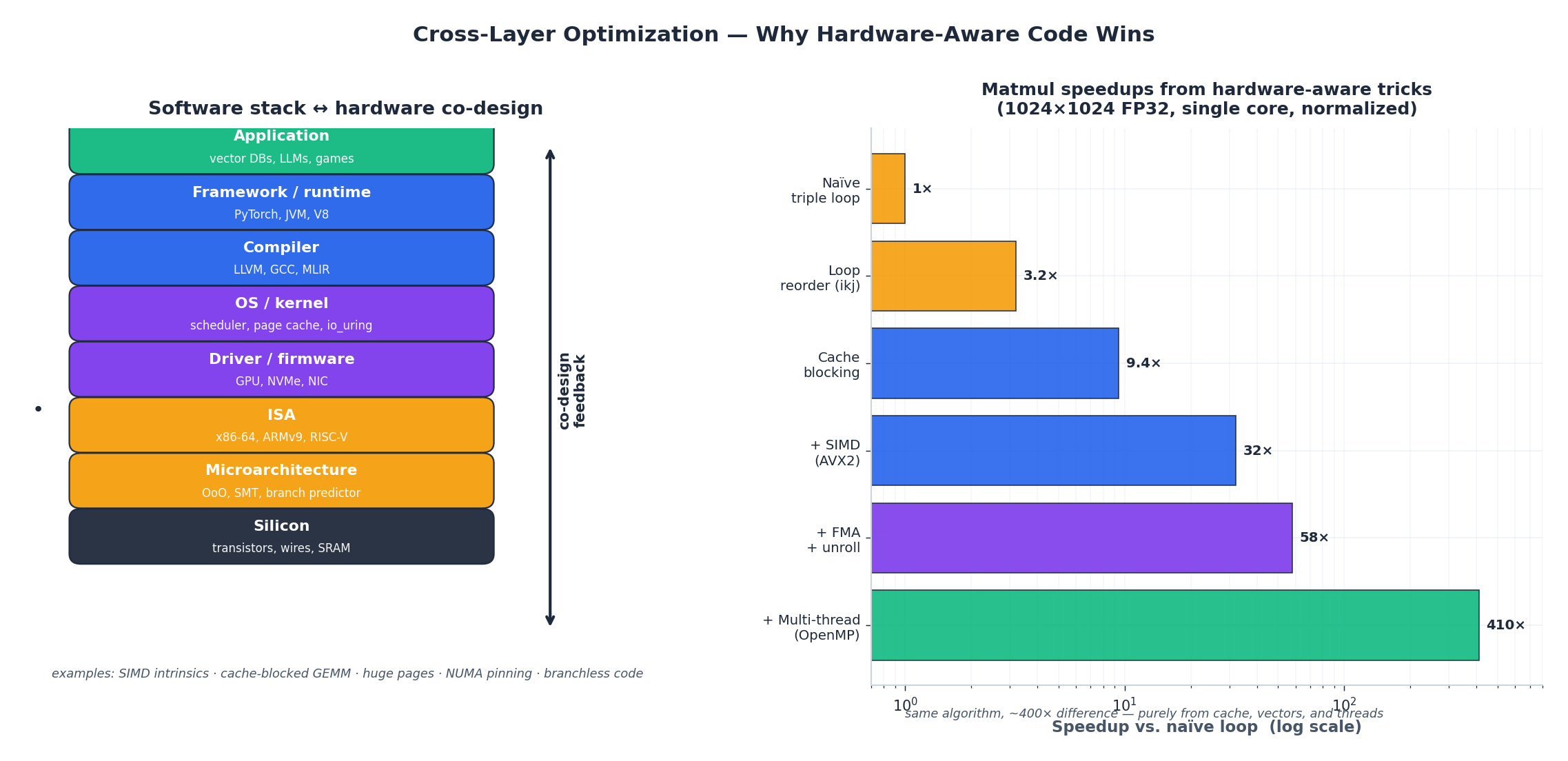

左边是你已经熟悉的软件栈——应用、框架、编译器、操作系统、驱动、ISA、微架构、硅。右边讲的是:当信息能够在这条栈里上下流动,而不是被一层层封死时,会发生什么。

那张柱状图是一个经典实验:单核、FP32、做一次 1024×1024 的矩阵乘。最朴素的三重循环是基线。把循环顺序换成 ikj,让最内层是单位步长,缓存就开始友好了,3× 加速到手。把矩阵分块以贴合 L1,到 10×。换成 AVX2 向量指令,到 32×。再加上 FMA 和循环展开,让乱序执行引擎有活干,到 58×。OpenMP 多线程铺到所有核上,400×。算法没变,FLOPs 没变。这 400 倍纯粹来自一件事:告诉硬件你到底想要什么。

这就是整个系列的核心结论。CPU 没慢,内存也没慢,慢的是大多数软件根本没让机器开起来。

有几条规律值得背下来,它们到处都会出现:

- 步长比次数更重要。 一个循环每条 cache line 只动一个字节,比每条 cache line 全动的循环慢 64 倍。

- 预测不准的分支,比"多干一点活"更可怕。 Branchless 代码、或者方向几乎固定的分支,往往跑赢"聪明"的捷径写法。

- 分配也是一次内存访问。 热循环深处的一次

malloc,可能比循环本身的工作还贵。 - 并发的瓶颈通常是带宽,不是 CPU。 八个线程抢同一条 cache line,比一个线程跑还慢。

工具其实都不花哨:perf、vtune、flamegraph、valgrind --tool=cachegrind。它们告诉你哪一行代码才是真正的瓶颈。而那一行,几乎从来不是你猜的那一行。

第三部分 —— 计数器:让机器自己告诉你它在干什么

每一颗现代 CPU 都自带一个性能监控单元(PMU)——一组小小的寄存器,用来计数微架构事件。它们就是"猜"和"测"之间的差别。

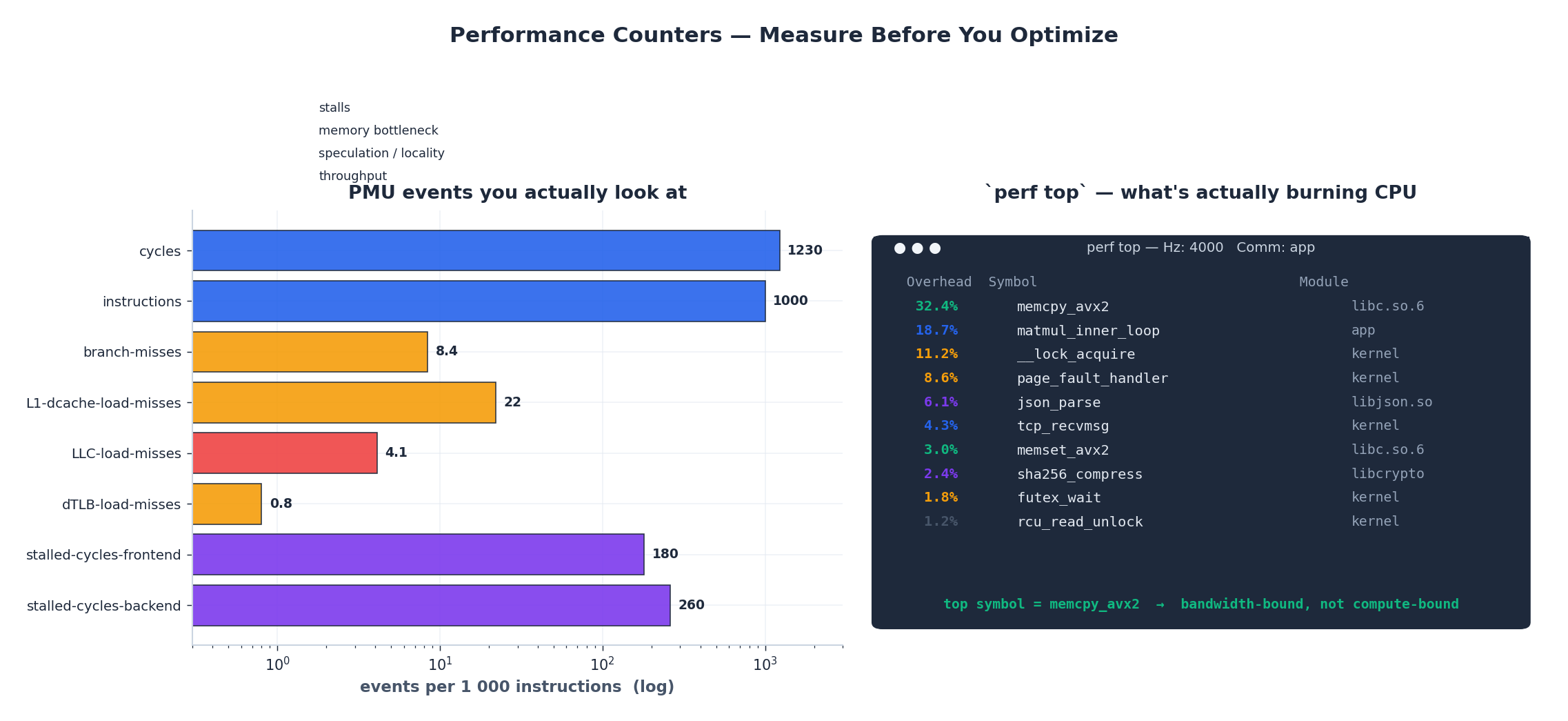

左边是你最常看的几类事件,按"每千条指令多少次"归一化。右边是一段典型热点工作负载下 perf top 的真实样子——一份正在烧 CPU 的符号实时榜单。

几条关键事件的速记:

cycles与instructions给出 IPC(每周期指令数)。现代 Intel/AMD 核心在没有 stall 时能跑到 3–4 IPC。如果你看到 0.3 IPC,那核心其实大部分时间都在发呆,问题大了。branch-misses一旦超过每千条指令 5 次,通常意味着某个热点分支预测不准。有时一个__builtin_expect就够,更多时候需要重排数据,让分支大部分时间走同一边。L1-dcache-load-misses和LLC-load-misses帮你定位缓存问题在哪一层。L1 miss 命中 L2 也就几个周期;LLC miss 打到 DRAM 几百个周期起步。一次 LLC miss 大约浪费一千条指令。dTLB-load-misses指向工作集超出 TLB 覆盖范围。常用解法是大页(huge pages)——一个 2 MB 大页能顶 512 个 4 KB 小页。stalled-cycles-frontend与stalled-cycles-backend告诉你核心是在等指令到位(前端,多半是 I-cache 或分支预测的锅),还是在等内存里的结果(后端,几乎一定是内存带宽的锅)。

那张模拟的 perf top 面板正好展示了第一次 profile 时最常见的意外:榜首的符号几乎从来不是你的业务逻辑。是 memcpy,是某个锁,是 page fault handler。真实程序首先撞到的是带宽墙和同步墙,远在撞到算力墙之前。 这不是你代码不行,这就是现代硬件的形状。

一个我从没失手过的工作流:

- 用一个紧密循环复现这个慢场景。

perf stat -d ./app:看 IPC、缓存 miss 率、分支 miss 率。perf record -g ./app && perf report:找出热点符号。- 用

perf annotate读这个符号的反汇编,看看采样集中在哪一行。 - 形成一个假设,改一个东西,回到第 2 步。

性能工作的大部分功夫,其实就是不肯跳过第 4 步。

第四部分 —— 冯诺依曼瓶颈:从前到现在

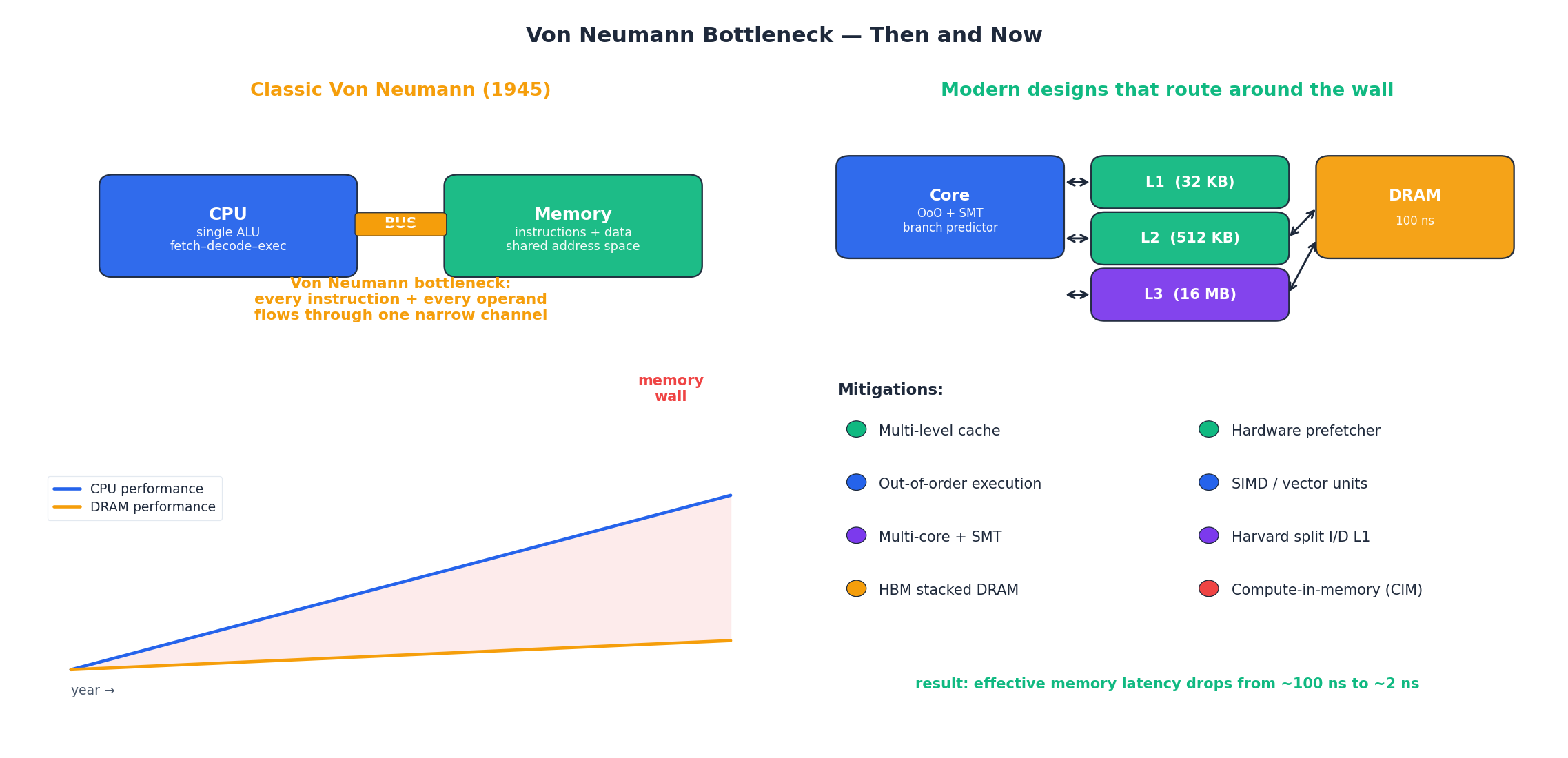

1945 年,约翰·冯诺依曼勾画了几乎所有现代计算机仍在使用的那张架构图:一个 CPU、一个内存、一条总线,指令和数据共享一个地址空间。这套设计漂亮、通用——也带着一条刻在骨子里的限制,从此塑造了整个计算行业。

左边就是那个经典问题。只有一条总线,CPU 执行的每一条指令都要从这条总线下来,每一个操作数都要从这条总线下来,每一个结果都要从这条总线上去。1990–2000 年代 CPU 主频一路狂飙,DRAM 速度却几乎原地踏步,两者之间那条不断拉大的鸿沟——memory wall(内存墙)——成为整个计算机性能的主导成本。今天,一条 cache 全 miss、最终打到 DRAM 的访存,相当于浪费 CPU 大约 300 条指令的工作量。

右边是过去五十年抗战的成果:

- 多级缓存 把更小、更快的内存副本塞进芯片内部。L1 命中只要 <1 ns,整个层级是 3 GHz 主频得以存在的前提。

- 硬件预取器 看你在线性走内存,主动提前加载。

- 乱序执行:等慢访存的同时,让核心继续推进那些独立的指令。

- SIMD:一条指令做 8 或 16 路浮点,把访存成本摊掉。

- SMT(超线程):给核心两条指令流可选,永远有活干。

- 哈佛式 L1 分离:指令缓存和数据缓存分开,前端后端可以并行取。

- HBM:DRAM die 直接堆到计算芯片上方,做到每秒 TB 级的带宽。

- 存内计算(CIM) 是最激进的一条:把算术做到内存阵列里,数据干脆不动。

合在一起的效果非常戏剧性。裸的 DRAM 延迟二十年来几乎没变,仍然在 80 ns 上下。但一个写得好的程序看到的有效延迟已经接近 2 ns——因为绝大部分访问都被缓存接住、被预取器提前抓到、或者藏在了乱序执行的影子里。我们没有打破内存墙,我们绕过了它。

理解这一点之后,你写代码的方式会变。纸面上最优的算法,在真机上可能因为乱跳内存而跑得很慢;纸面上很浪费的算法(多一些算术、多一些重复加载),却可能因为始终待在缓存里而跑得飞快。 现代性能是一场伪装成算力游戏的内存游戏。

第五部分 —— 异构计算:每件事用最合适的工具

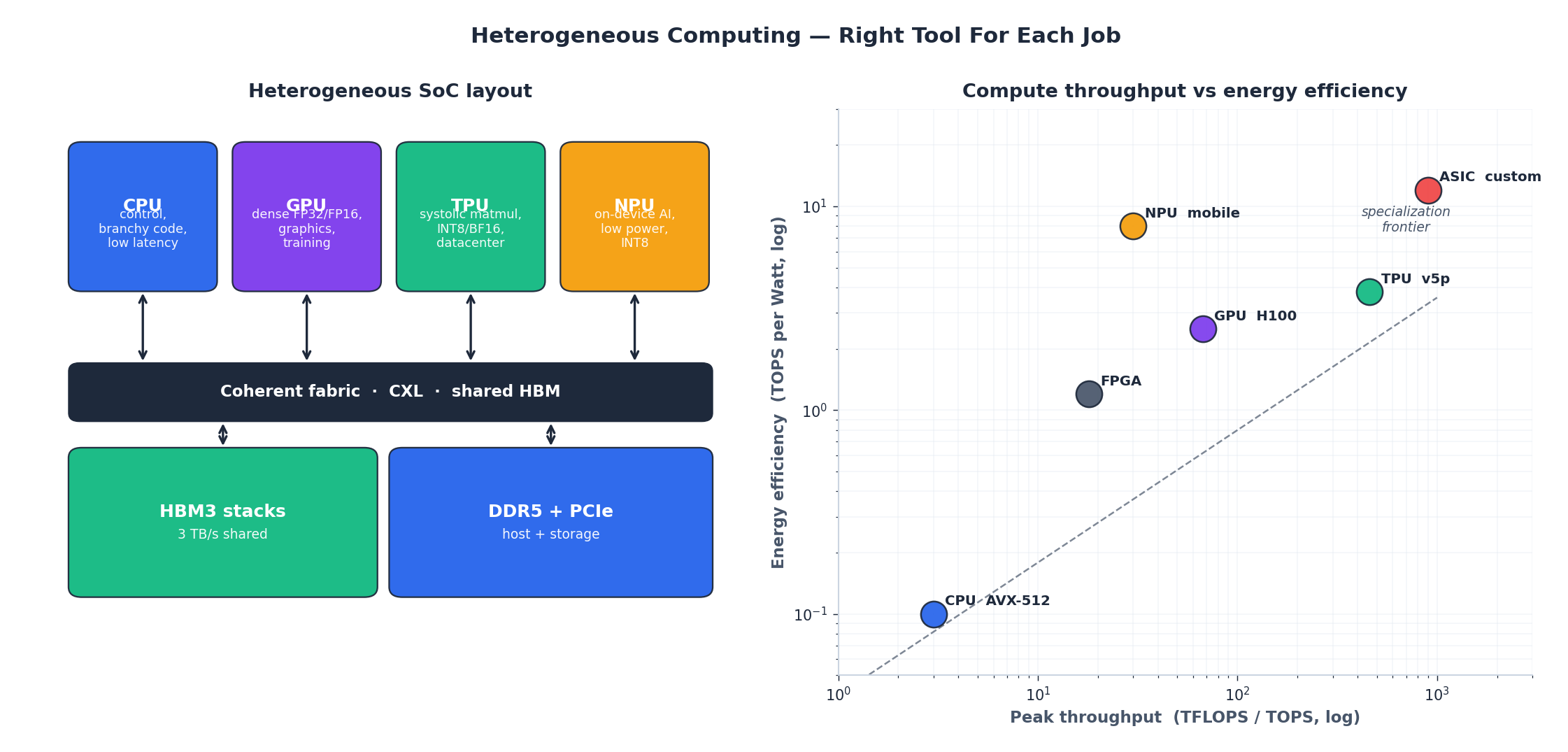

几十年里,“计算机"基本等同于 CPU,每个工作负载都得交同样的架构税。这个时代正在结束。2026 年的一台笔记本,CPU、GPU、NPU、视频编解码块、安全 enclave 都在同一颗 die 上;数据中心的一个机架里有 CPU、GPU、TPU、FPGA、SmartNIC,真正有意思的问题不再是"你的 CPU 多快”,而是"你把这个负载放对地方了吗”。

左边是一颗现代 SoC 真正的样子。专用 tile —— CPU 跑控制流、GPU 跑稠密浮点、TPU 跑 INT8 矩阵乘、NPU 跑低功耗端侧 AI ——共享一条一致性总线和一池 HBM。这条总线正在通过 CXL 跨封装延伸出去,让不同插槽里的加速器也能共享内存,不用在软件里打转。

右边把这个权衡讲得更直接。横轴是峰值吞吐(TFLOPS / TOPS,对数刻度),纵轴是能效(每瓦 TOPS,对数刻度)。几个收获:

- 一颗带 AVX-512 的现代 CPU:几个 TFLOPS、约 0.1 TOPS/W。处理分支多、对延迟敏感的代码非常出色,干矩阵乘则极其浪费。

- 数据中心 GPU H100:约 67 TFLOPS、2.5 TOPS/W。通用到能训练任何你写得出的神经网络,快到足以成为训练默认选项。

- TPU v5p:吞吐大约 7×、能效约 1.5× —— 但前提是你的负载长得像一个巨大的脉动阵列矩阵乘。

- 手机端 NPU 在能效上能赢 CPU 80×,所以你的手机能一边实时识别语音一边电量不掉。

- 定制 ASIC 站在前沿曲线上:吞吐顶满、能效顶满、灵活性几乎为零。比特币挖矿、视频编码、网络包处理。

那条虚线"专用化前沿"是一条真实的曲线。每往专用化方向走一步,吞吐和能效就上升一格,通用性就下降一格。 没有免费午餐,只有一份菜单,工程的本事在于点对菜。

实操建议很短:先 profile,再选硬件,再选算法。把一个分支密集的图遍历放到 GPU 上,跟在 CPU 上跑 BERT 一样浪费。

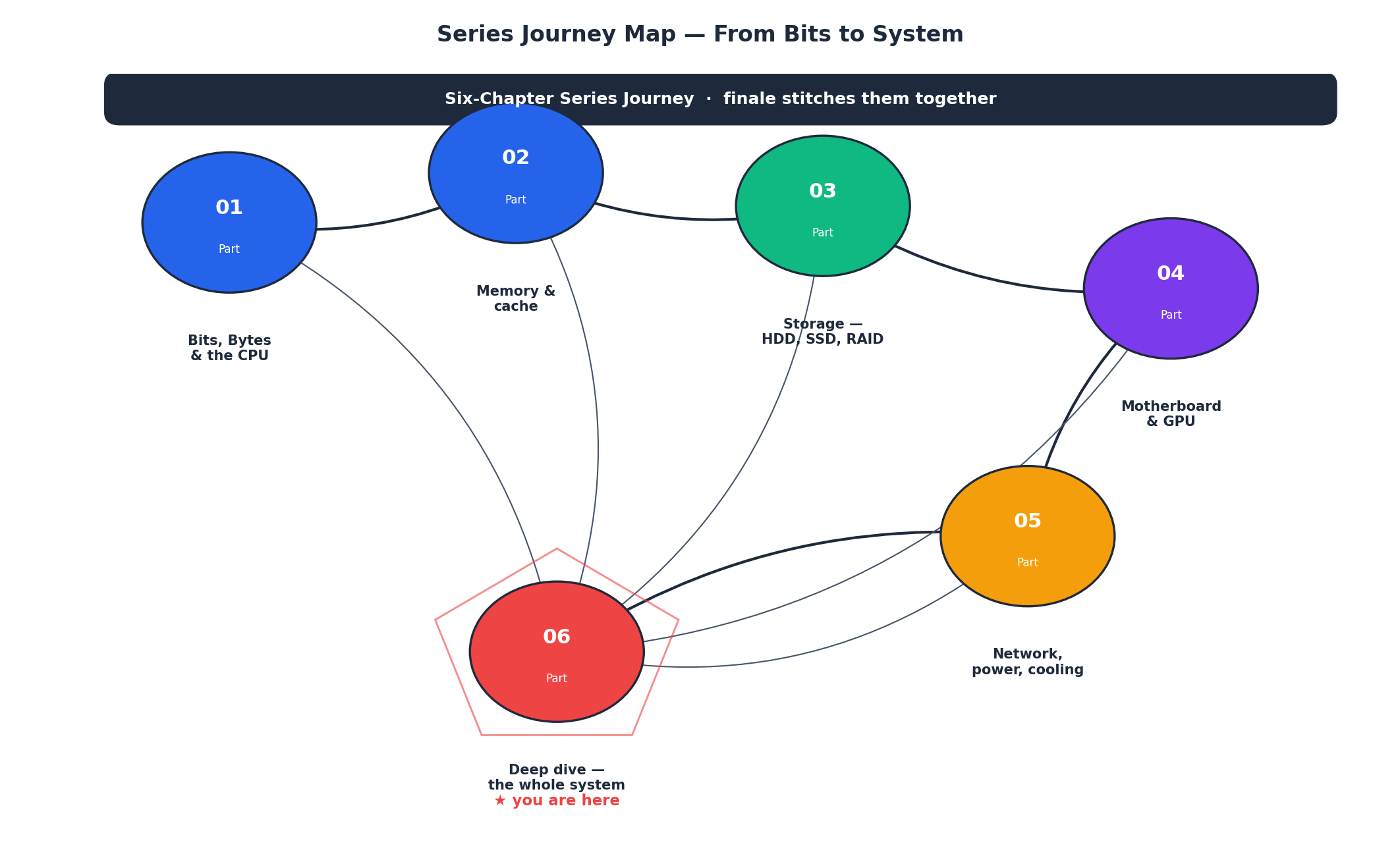

第六部分 —— 一段旅程:从比特到系统

把技术细节放下,回头看这个系列走过的路。每一章搭一块脑中的模型,这一章把它们连起来。

- 第一章 —— 比特、字节与 CPU。 我们从一切的起点开始:一比特两个状态,一字节八比特,ASCII 把英文装进来,UTF-8 把世界装进来。然后走进 CPU 本身:核、线程、主频、Intel 与 AMD 的差别、为什么 32 位系统认不出 4GB 以上内存。

- 第二章 —— 内存与缓存。 DDR 各代演进、双通道、三级缓存层级、命中率、为什么加通道往往比加频率更划算。

- 第三章 —— 存储。 HDD 的盘片与磁头、NAND 闪存从 SLC 到 QLC、SATA 与 NVMe、RAID 等级、从 DRAM 到 Glacier 的存储分层金字塔。

- 第四章 —— 主板与显卡。 芯片组、PCIe 通道与代际、M.2 槽布线、VRM 相数、GPU 的内存层级、撑起大规模并行的 SM/CUDA core 架构。

- 第五章 —— 网络、电源、散热。 网卡速度与 RDMA、OSI 模型在工程里怎么用、电源功率与 80 PLUS、风扇曲线与温度墙、整机装机清单。

- 第六章 —— 也就是这一章。 整台机器、跨层优化、性能计数器、冯诺依曼的故事、异构计算,以及接下来发生的事情。

每一部分都是一块砖,没有哪一块本身就是房子。房子是你正坐在面前的那台机器,而六块砖能同时入眼的那一刻,就是硬件不再神秘的那一刻。

第七部分 —— 接下来:chiplet、硅光、量子

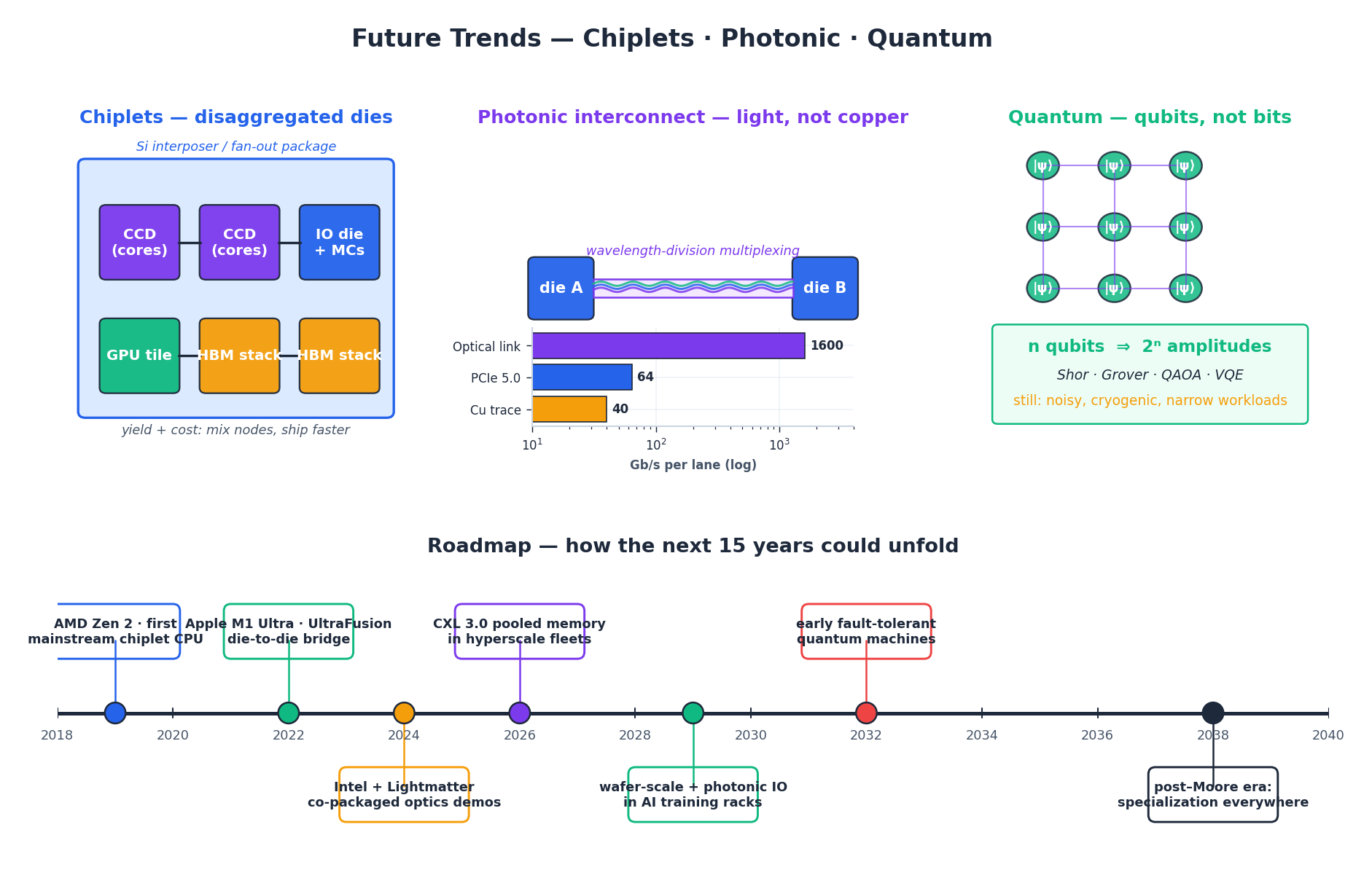

媒体口中的摩尔定律——同一颗单片 die 上晶体管数每两年翻一番——已经结束了。晶体管还在缩,但经济性、良率和物理都不再支撑无限放大的单片芯片。真正有意思的问题是:什么会接替它? 三条线索已经清晰可见。

Chiplet —— 把一颗大 die 拆成共享封装的小 die。 不再要求一颗 600 mm² 的巨型 die 完美良率,而是把封装造成由若干小 chiplet 拼起来的房子,每块 chiplet 都用最适合它的工艺去流片。AMD 的 Zen 2 是 2019 年的主流首秀——独立的 CCD 加 IO die,靠 Infinity Fabric 通信。苹果 M1 Ultra 用 UltraFusion 把两颗 M1 Max 粘在一起。Intel Meteor Lake 把 CPU tile、GPU tile、SoC tile、IO tile 拼在同一个封装里。好处是经济账上的暴力胜利:一颗 600 mm² 单片 die 良率惨淡;六颗 100 mm² chiplet 良率舒服,可以混搭,还能让不同部分跑在不同工艺节点上。代价是互连——这些 chiplet 之间必须低延迟、高带宽地说话,所以 UCIe(Universal Chiplet Interconnect Express)这种标准突然变得很急。

硅光互连 —— 用光不用铜。 铜走线在每通道几十 Gb/s 之后就撞墙,信号完整性会崩。光不会。Co-packaged optics 把一颗微型激光器和波导直接放到计算 die 旁边,再用波分复用让一根光纤同时承载几十路通道。最早的应用场景是"逃出封装”——把数据从 GPU 封装里送出去,喂饱跨越上千张加速卡的 AI 训练 fabric。Lightmatter、Ayar Labs,加上各家超大规模云厂商都在做,2024–2026 年开始有商用部署落地。到 2030 年前后,它很可能就是高端芯片对外通信的默认方式。

量子 —— 不是比特,是量子比特。 一个 qubit 不是更快的 bit,而是另一种东西。n 个 qubit 同时承载 2ⁿ 个振幅,量子算法通过干涉把这些振幅引导向答案。对一类很窄的问题——大数分解(Shor)、无序搜索(Grover)、部分化学和优化问题——这意味着指数级或平方级的加速。当前的硬件嘈杂、低温、规模小。所有人正在赛跑的那个 2032 年前后的里程碑叫容错量子计算——qubit 足够多、纠错足够强,足以在真实输入上跑那些著名的算法。它不会取代你的笔记本,它会取代某些今天根本算不动的特定计算任务。

图的下半部分把这三条线索拉到一根时间轴上。大局是:未来十五年的计算不会是一次大跳,而会是许多小跳,全都朝着"专用化"方向走——定制硅、定制互连、定制物理——靠真正了解底层的软件把它们粘合起来。

收尾 —— 拿这些做点什么

到这里,你已经把这台机器从头到尾看了一遍。下面几个习惯,会让这份知识在未来很多年里替你复利:

- 东西慢的时候,先量再猜。 一次

perf stat加一张 flamegraph,能省下几天错误直觉的时间。 - 读你手上这台机器的 datasheet。 缓存大小、内存通道、PCIe 通道接到哪里——都写在里面,你看到的大部分现象都能从那里解释。

- 维护一个心智模型,不断打磨它。 每一项新技术——CXL、硅光 IO、MI300 chiplet——都能放进第一部分那张系统图的某个位置上。找到它放在哪里,你就理解了它。

- 写一点真正压硬件的东西。 一个玩具数据库、一个小光线追踪器、一个你自己的 profiler。看着 IPC 因为你改的某一行代码,从 0.3 跳到 2.8——没有任何东西能替代那一刻。

计算机硬件不是一份购物清单,而是一套被八十年、几万名工程师一寸一寸打磨出来的系统,是人类造过的最精巧的机器。理解它怎么工作,是你能掌握的、杠杆率最高的知识之一。

谢谢你陪到了这一章。下一个系列见。

—— 计算机基础系列 · 完 ——